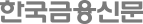

△5월 14일(현지시간) 미국 산타클라라에서 열린 '삼성 파운드리 포럼 2019'에서 정은승 삼성전자 파운드리 사업부 사장이 기조 연설을 하고 있다/사진=오승혁 기자(자료 편집)

이번 포럼에는 작년보다 약 40% 증가한 500명 이상의 팹리스 고객과 파운드리 파트너가 참석했다. 또한, 첨단 파운드리 기술 트렌드를 공유하는 전시 부스 운영에도 참여 기업이 두 배 가량 증가해, 삼성전자의 반도체 비전 2030 선포 이후 높아진 국내 시스템 반도체 업계의 관심을 확인할 수 있었다.

삼성전자는 올해 4월, 133조 원 투자와 1만5000명 고용 창출을 통해 2030년까지 시스템 반도체 글로벌 1위를 달성하겠다는 반도체 비전 2030을 선포한 바 있다.

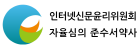

삼성전자는 이번 포럼에서 AI, 5G, 전장, IoT 등 4차 산업혁명 시대를 주도할 최신 EUV 공정 기술부터 저전력 FD-SOI, 8인치 솔루션까지 폭 넓은 파운드리 포트폴리오를 소개했다.

정은승 삼성전자 파운드리사업부 사장은 기조연설에서 "삼성전자는 반도체 불모지에서 사업을 시작해 역경을 딛고 업계 1위에 오른 경험이 있다.”며, “파운드리 분야의 최고를 향한 여정도 쉽지 않겠지만 난관을 헤치고 함께 성장해 나갈 수 있게 관심과 응원을 부탁 드린다"고 말했다.

이외에도 "국내 팹리스 기업들이 신시장을 비롯한 다양한 분야에서 활약할 수 있도록 디자인 서비스, 제조, 패키지 등 개발부터 양산까지 협력 생태계를 활성화해 시스템 반도체 산업 발전에 기여하겠다"고 밝혔다.

△5월 14일(현지시간) 미국 산타클라라에서 열린 '삼성 파운드리 포럼 2019'에서 글로벌 팹리스 고객, 파트너사 등 참석자들이 정은승 삼성전자 파운드리 사업부 사장의 기조 연설을 듣고 있다/사진=오승혁 기자(자료 편집)

이미지 확대보기이장규 텔레칩스(팹리스 반도체 업체) 대표는 “올해 스무살이 된 텔레칩스는 삼성의 파운드리 기술 발전과 함께 성장해 왔다고 해도 과언이 아니다”며, “뛰어난 제품으로 시장 경쟁력을 더욱 높여 가기 위해 현재 협력 중인 14나노에 이어 10나노미터 이하 미세 공정에서도 탄탄한 협력을 이어 나갈 계획이다”라고 말했다.

삼성전자는 국내 팹리스 기업에게 7나노 이하 EUV 기반 초미세 공정도 적극 제공해 차세대 첨단 제품 개발을 지원함으로써 국내 시스템 반도체 산업의 경쟁력 확보에도 기여해 나갈 계획이다.

또한 팹리스 고객들이 삼성의 파운드리 공정 기술과 서비스를 보다 쉽게 활용할 수 있도록 반도체 디자인하우스를 비롯해 설계자산(IP), 자동화 설계 툴(EDA), 조립테스트(OSAT)까지 국내 파운드리 파트너들과 협력을 확대해 나갈 예정이다.

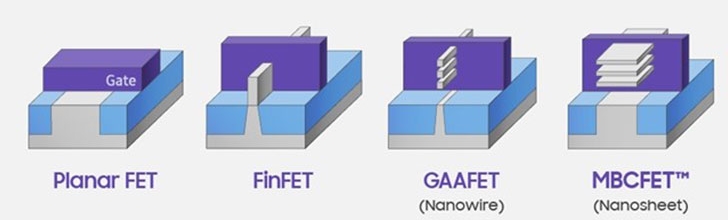

한편 삼성전자는 2019년 4월, 저전력 28나노 FD-SOI 공정 기반 eMRAM 솔루션 제품과 EUV 노광 기술을 적용해 성능과 수율을 높인 7나노 핀펫 제품을 출하와 차세대 5나노 공정 개발을 공개하는 등 파운드리 기술을 선도하고 있다.

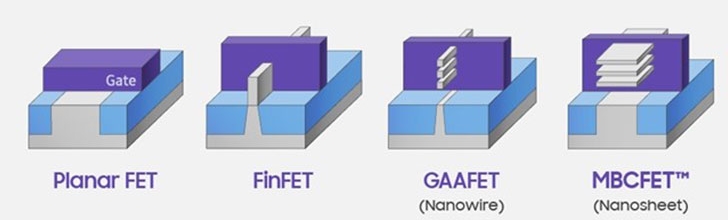

특히, 전류가 흐르는 통로인 원통형 채널 전체를 게이트가 둘러싸 전류의 흐름을 더 세밀하게 제어할 수 있는 차세대 트랜지스터 구조의 3나노 GAE(3나노 Gate-All-Around Early) 공정 설계 키트(PDK v0.1, Process Design Kit)를 팹리스 고객에게 배포하기도 했다.

오승혁 기자 osh0407@fntimes.com

![[DCM] '금리 충격' 롯데그룹, 전방위 구조조정∙자산매각 불가피](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=69&h=45&m=5&simg=2024112521455208787a837df64942192515869.jpg&nmt=18)

![4대 금융 CEO 37명 임기 만료…인사 태풍 ‘촉각’ [연말 금융 인사 미리보기]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=69&h=45&m=5&simg=2024112607143100418f09e13944d391241172.jpg&nmt=18)

![[DCM] DL, 유동성 확보 총력…여천NCC는 ‘발목’](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=69&h=45&m=5&simg=2024112601153906131a837df64942192515869.jpg&nmt=18)

![이재근·김성현·이창권·이환주 등 인사 대상…‘취임 2년차’ 양종희 회장 선택은 [연말 금융 인사 미리보기]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=69&h=45&m=5&simg=2024112621442006457f09e13944d582914364.jpg&nmt=18)

![이재근 행장 필두 부행장 24명 전원 임기 만료...국민은행 인사 행방은[연말 금융 인사 미리보기]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=69&h=45&m=5&simg=2024080716110804667c1c16452b0175114235199.jpg&nmt=18)

![미래에셋운용, 글로벌 전진기지 배치로 순익 1위 견고…'ETF 효과' 신한운용 2위 [금융사 2024 3분기 실적]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=69&h=45&m=5&simg=2024112710225906906179ad4390712813480118.jpg&nmt=18)

![[카드뉴스] 국립생태원과 함께 환경보호 활동 강화하는 KT&G](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=298&h=298&m=1&simg=202403221529138957c1c16452b0175114235199_0.png&nmt=18)

![[카드뉴스] 신생아 특례 대출 조건, 한도, 금리, 신청방법 등 총정리...연 1%대, 최대 5억](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=298&h=298&m=1&simg=20240131105228940de68fcbb35175114235199_0.jpg&nmt=18)

![[카드뉴스] 어닝시즌은 ‘실적발표기간’으로](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=298&h=298&m=1&simg=202311301105084674de68fcbb35175114235199_0.png&nmt=18)

![[신간] 사모펀드 투자와 경영의 비밀](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=81&h=123&m=5&simg=2024102809331308730f8caa4a5ce175114235199.jpg&nmt=18)

![[신간]퍼스널브랜딩, 문학에서 길을 찾다](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=81&h=123&m=5&simg=2024102214123606876f8caa4a5ce175114235199.jpg&nmt=18)

![[서평] 추세 매매의 대가들...추세추종 투자전략의 대가 14인 인터뷰](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=81&h=123&m=5&simg=2023102410444004986c1c16452b0175114235199.jpg&nmt=18)

![[신간] 김국주 전 제주은행장, ‘나는 시간을 그린다 1·2’ 에세이 출간](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=81&h=123&m=5&simg=2024111517430908074c1c16452b012411124362.jpg&nmt=18)